Hello everyone,

Edit: I am using version 0.33, installed via apt install (Ubuntu/WSL).

I’m working on a project that uses Yosys to analyze synthesized circuits. I’m taking RTL designs (in my case, a parameterized FIR filter in SystemVerilog originally built and simulated in Vivado) and converting them to a gate-level JSON using Yosys for downstream analysis.

Here’s my challenge:

after running passes like

read_verilog fir_test.v

hierarchy -top kepq4

proc; opt; flatten

techmap -autoproc -map +/xilinx/cells_sim.v

opt; aigmap

write_json yosys_out.json

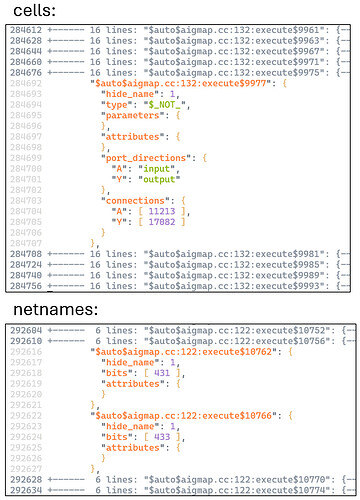

the resulting $and and $not cells in the final JSON have lost nearly all human-readable context. Importantly, I can no longer tell which RTL component or vendor primitive (e.g., LUT2, CARRY4, FDCE) each gate originally came from. The src attribute usually points to internal Yosys source files (like aigmap.cc) rather than the original Verilog locations. The parameters and attributes fields are empty.

My goal is to preserve or reconstruct the “history” of each synthesized node and ideally to be able to determine which original component the node originated from (i.e. this particular AND gate comes from a the LUT2 primitive, etc.).

So I’m wondering:

-

Is there a recommended or supported way to preserve RTL provenance through synthesis and techmap/aigmap passes?

-

If not, are there any practical workflows or passes that can help me embed or extract this mapping (perhaps with attributes or a debug dump before/after major transformations)?

-

How do others handle this problem when they need traceability from AIG or gate-level structures back to RTL or vendor primitives?

Apologies if this has been asked before. I’m a new user of Yosys and am still learning.

Any advice or pointers would be greatly appreciated.

Example screenshots from the yosys output json. Included screenshots from cells and netnames.